计算机基础——计算机组成原理(b栈视频版)

写在最前面:本篇文章会分章节简要介绍一下计算机组成原理的相关知识,从计算机硬件依次进行介绍,并最终在xxxx中动手制作一台计算机。(以描线的方式)

前情提要:需要先了解二进制与编码相关知识,对于逻辑运算和逻辑门等要知晓,对于算术逻辑单元ALU的组成和功能有所了解。

寄存器 & 内存

前面已经:学习了ALU,下面就要学习使用ALU制作CPU。但是在此之前,计算机还需要一些“记忆”,也就是内存。

锁存器

一个基础的电路抽象,可以存储单bit数据,相当于

造房子的砖头。下面会从最基础的单门电路进行介绍,而后进行组合、简化、封装得到需要的原件。

上述OR电路可以永久存储1,无论输入怎么变都不会改变输出。

上述AND电路可以永久记录0,无论输入怎么改变都不会改变输出。

将OR和AND结合起来就可以设计出锁存器:一个可以存储单bit的电路。

其中:如果“设置”为1,“复位”为0,则输出为1;如果“复位”为1,则输出为0;如果二者都是0,则输出为最后放入的内容。

将输入线简化为一条,即可得到上图所示:“允许写入”为1,存储的值会以输入为准;“允许写入”为0,则输出为固定值,不会受到输入的影响。

再次进行抽象:将复杂的逻辑电路封装为一个box,只关注其功能,而不关心其实现,即可得到一个可以存储单bit数据的锁存器。

寄存器

一个只可以存储单bit数据的锁存器是没有用的,但是将多个锁存器组合就可以存储多bit数据,组合后的锁存器叫做寄存器。

位宽

寄存器可以存储多少数据取决于其由多少锁存器组合,我们将其叫做位宽。现如今我们使用的个人笔记本多为64位位宽,也就是说寄存器有64个锁存器组合获得。

组成原理

下面我们将介绍一下寄存器的组成原理与优化方案

一个简单的8位寄存器的组成如下:

如图所示,通过八个并列排放锁存器即可实现寄存器的功能:首先将所有的E置1用于数据存入,而后通过线连接D、Q端获取输入输出。

但是,只是存储一个8bits数据就要17根线(E口只需要一条线即可),如果要存储更多位数据就需要更多的线,这显然不符合我们设计预期。

当然,解决方法也很简单:矩阵!

优化方案:矩阵

如图所示,锁存器不再并列排布,而是通过矩阵的方式进行。要启动某个寄存器就只需要打开对应的行线和列线即可。

我们来细看其实现原理:

通过一个AND门实现启动功能,只有当行线和列线都为1时才启动此锁存器。

而后通过一条允许写入线连接所有锁存器,一根数据传入线来传输数据,一根数据传出先来获取数据。

通过矩阵处理后,原本存储256bits数据需要513条线,而现在只需要35根线(3+32)

多路复用器

将地址转换为行和列,已确定正确的存储地址。

如上图所示,即为多路复用器。其作用就是把给定的地址转换为具体的坐标,以定位到确定的锁存器。

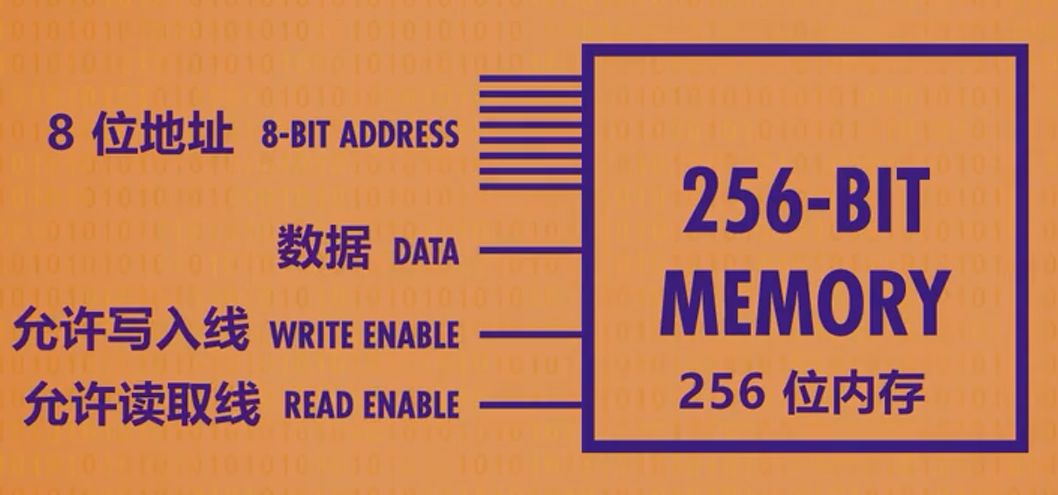

此图看起来比较复杂,所以我们需要进一步抽象,得到更加直观的模型。抽象后的模型如下:

将256位内存看作一个整体,而后给出具体的判断条件即可。

内存(RAM:随时存取存储器)

上文讲到了256位的存储器,通过矩阵排列的锁存器得到。但是256位也太小了,为了扩大存储容量,就需要继续进行组合。下面我们具体进行介绍。

将前面所抽象得到的256位存储器进行排列,并通过线将其连接即可构成一个新的存储空间。

我们先来介绍一下使用的线:

首先需要8位的地址线,用于定位到具体的锁存器;之后是允许写入线和允许读取线各1条,控制此存储器的读写性;最后是8条数据线,用于写入和读取数据。

继续进行抽象

由于上图过于复杂,虽然可以清晰的表示出数据的存储方式与位置,但是却不契合人类的思维方式,而人类更加适应的数据获取方式当然就是:将内存地址从小到大标号,通过此标号来标明位置。因此,一个整体的可寻址内存就出来了。

如图所示,不再考虑内部实现方式,而是将其转换为了符合人类思维方式的表示方法。

继续扩展

现代计算机的内存已经扩展到了MB、GB的方式,但是其实现方式大同小异:不断把内存打包到更大规模而后使用一个直观的模型表示即可。

当然,随着内存规模的不断扩大,需要的内存地址也要增加。原先的8位内存地址最多可以表达256个内存地址(以字节为单位,因为前面8个并排的256存储器接收到的内存地址是一样的,所以内存地址的最大值就是矩阵中锁存器数目)而要给更多的内存寻址,就需要更大的内存地址,现在比较通用的是32位和64位。

补充知识:RAM和ROM的区别(转)

我的思考:

通过对计算机内存的学习,我越发感到其中的精妙与博大精深。

从最底层的门电路出发,构造可以存储单bit的电路,之后组成锁存器。

之后通过对多个锁存器的不同排列得到可以存储多bit的存储器。这其中利用矩阵的方式,借助多路复用器寻址。

构成的多bit单元又可以继续进行组合得到可以存储更多数据的存储器。

如果单独查看每一个存储单元,会发生其结构很简单;难的是巧妙的抽象,由小及大、层层递进,每一层不需要关注底层的具体结构。

其实如果对计算机的基础知识进行学习,会发现这种分层思想无处不在,不仅仅是在这种硬件的排布封装上,操作系统的层次结构、计算机网络的层次结构等都有体现。

中央处理器

CPU:central precessing unit

前面我们学习了ALU、寄存器、RAM,现在要把这些进行组合,得到:计算机的心脏——CPU.

CPU的功能

执行程序:指令和数据。

指令包括数据的运算、数据的读取等。

其中指令由操作码和地址组成,前者告知要执行什么操作、后者告知操作的数据来自哪里(寄存器或者内存)

CPU的工作流程

下面我们以一个简单的程序为例来介绍一下CPU的工作流程。

将以功能为主线进行介绍,而不是一根根线具体怎么练(具体的连线会在笔记中介绍)

先来看一下要是使用的指令

一个有4个基础指令,需要记住其操作码和功能。

下面给出CPU的基本结构(简化版)

大概分为3个部分:寄存器、控制单元和算术逻辑单元

- 寄存器:用于存储数据,这里以8位寄存器为例。

- 控制单元:由指令寄存器和指令地址寄存器组成,其中指令寄存器存放当前指令,指令地址寄存器存储指令地址。

- 算术逻辑单元:即ALU,用于运算和逻辑处理。

接下来介绍一下cpu执行指令的三个阶段

取指令阶段:指令地址寄存器中存储指令地址,会根据此地址找到对应的内存位置并将此位置存储的数据放到指令寄存器里。指令解码阶段:由控制单元解析指令寄存器里的指令,解析的方法是通过电路实现的,具体见下图。

通过将前4位数据传入逻辑门电路而后根据结果即可判断其指令。指令执行阶段:根据解码的结果进行指令的具体实现即可。我们下面使用到的指令大概分为以下3个类型

1)RAM到寄存器:如LOAD_A=0010,就是将对应内存地址中的数据存储到寄存器A中。

2)寄存器到RAM:如STORE_A=0100,就是将A寄存器里的数据放到对应内存空间。

3)寄存器到寄存器:如ADD=1000,就是将两个寄存器中的数据进行相加。

指令解析过程中的注意事项

指令解析是由CPU通过配置的检测电路来进行的,具体实现是将指令前4位数据传入所有的检测电路,而后输出为1的电路即为检测结果。

注:所谓解码并不是指让CPU知道这个指令的作用,而是会在解码电路之后通过线连接RAM和寄存器,通过控制这两个部分的允许写入和允许读取来进行具体功能的实现。

指令执行过程中的注意事项

上图给出了指令执行过程的流程图,注意你标黄的线。

首先会根据指令的解析结果将RAM的允许读取打开,而后通过指令寄存器中存储的后4位数据找到对应内存位置。

检查电路启用寄存器A的“允许写入线”,然后RAM通过data线将数据传入寄存器(

所以的寄存器都会接收到,但是只有允许写入的才会修改内容)指令执行完毕后可以关掉所有的线路。

时钟信号

上文我们介绍了cpu执行指令的流程,我们将每一个流程的实现看作一个周期,而cpu执行指令的快慢可以根据1秒钟的周期数来看。所以CPU引入一个时钟信号,控制单元会使用这个信号推动CPU内部操作。

时钟信号的单位是赫兹,1赫兹表示1秒1个周期。

高级CPU的设计

上文介绍了CPU的简单执行流程,其中涉及到了时钟信号,用于表示执行指令的快慢。随着技术的不断发展,时钟信号也在不断加快。下面我就介绍一下CPU为了实现高速、稳定运转而实现的高级设计吧。

指令数目的不断提升

我们前面介绍了4条基础指令,但是一个CPU中的指令不仅仅只有这4条。

第一个集成cpu就拥有46条指令,并且随着技术发展这个数目越来越多,到如今一个现代处理器往往有上千条指令。

指令的增多虽然可以实现更多功能,但是也带来了很多问题,包括:时钟信号的不断加快、RAM读取数据的延迟等。

高速缓存

前面我们讲过,cpu通过总线与RAM进行交互以读取学习,但是即便是总线很短、信号传输很快,在每秒数10亿的指令面前很小的延迟也会带来大问题。

解决延迟的一个方法就是给CPU加一点RAM——缓存。

缓存不会很大,往往是以KB、MB为单位,而RAM都是GB为单位。

缓存的作用就是在cpu从RAM取数据时不会只拿一个,而是拿一批。因为数据常常是顺序处理,所以缓存的机制可以提高cpu的执行效率,因为缓存与CPU很近,一个时钟周期就可以给数据。同时在存储数据时也不会直接存储到RAM,而是先存储在缓存里。

缓存中每一个存储空间会有一个标记:脏位,用于标记此空间内容是否被修改。当缓存满时要清空缓存,此时会先检查脏位,将有改动的数据线同步到RAM后再进行清除。

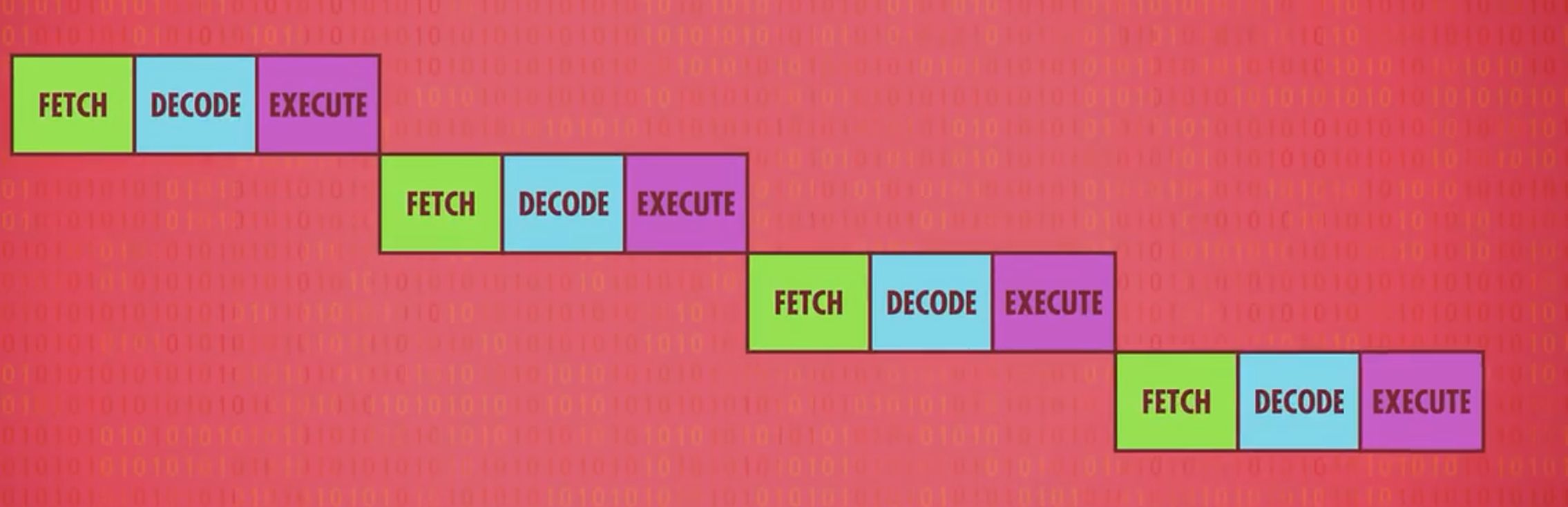

指令流水线

观察上述图片,比较其不同之处:指令的并行操作。在cpu执行指令时进行下一条指令的解码和下下条指令的读取。

写在最后:本次计算机组成原理部分到此结束。主要对CPU和RAM进行了介绍,更多涉及到底层实现和功能流程,还有很多内容内容没有介绍。在笔记中会以连线的方式从另一个角度介绍计算机组成原理。